3.1.1 简单门电路

门电路是构成所有组合逻辑电路的基本电路,因此在进行比较复杂的组合逻辑电路描述之前,先要掌握这些基本电路的VHDL描述。下面介绍一些常用的门电路的VHDL描述实例。

1.非门电路

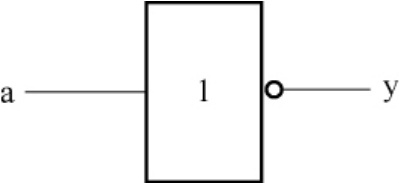

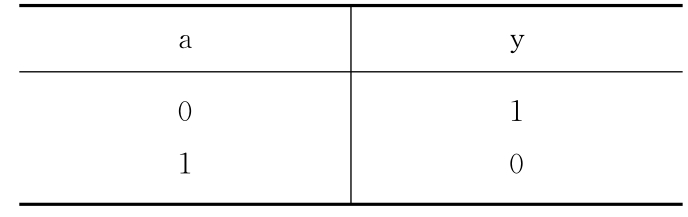

非门的逻辑表达式为:y=a,其逻辑电路图如图3-1,真值表如表3-1。

图3-1 非门的逻辑电路图

表3-1 非门的真值表

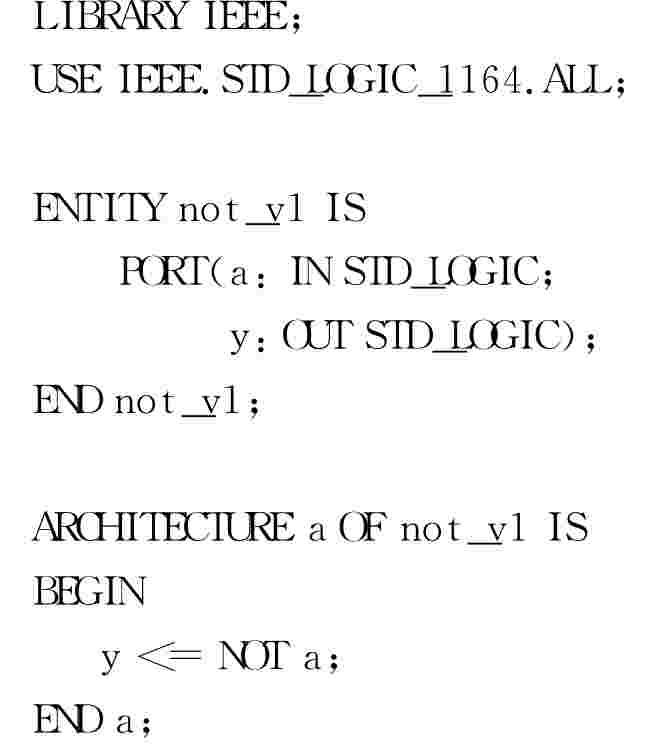

(1)非门的数据流描述

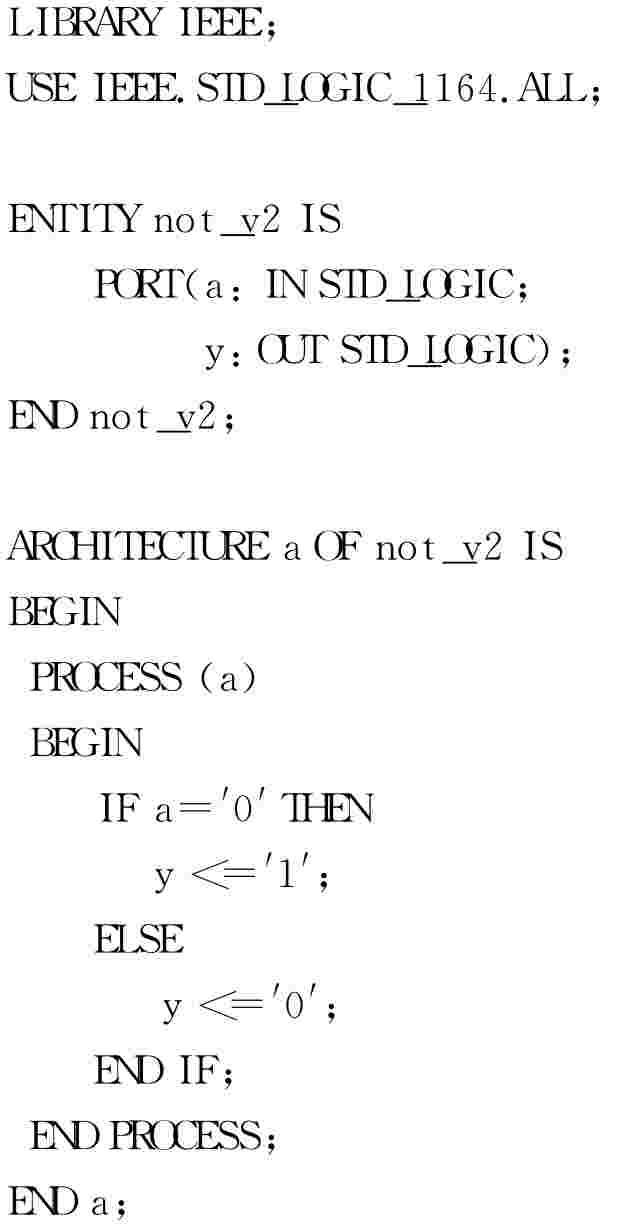

(2)非门的行为描述

2.两输入与门电路

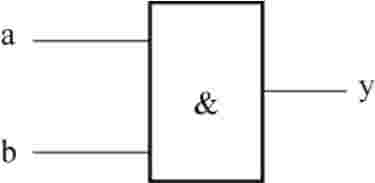

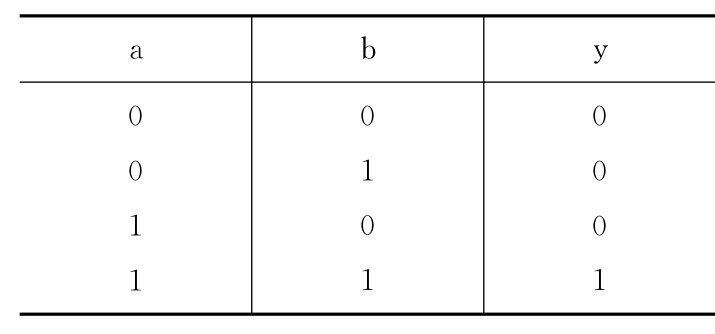

两输入与门的逻辑表达式为:y=a·b,其逻辑电路图如图3-2,真值表如表3-2。

图3-2 两输入与门的逻辑电路图

表3-2 两输入与门的真值表

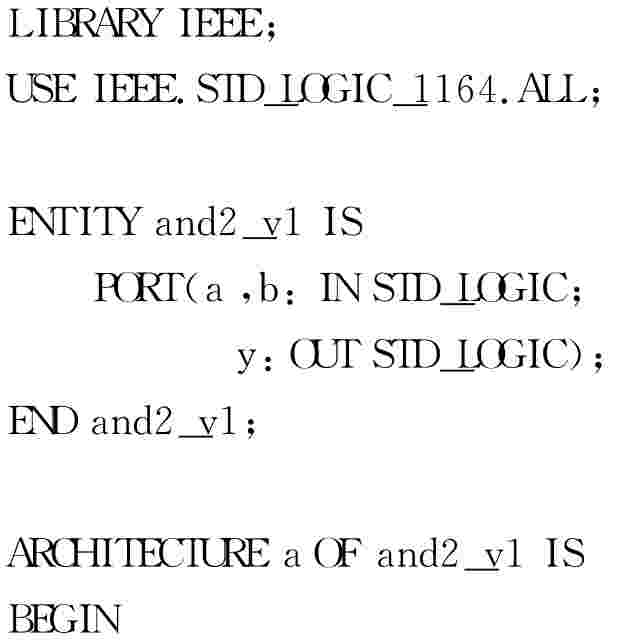

(1)两输入与门的数据流描述

![]()

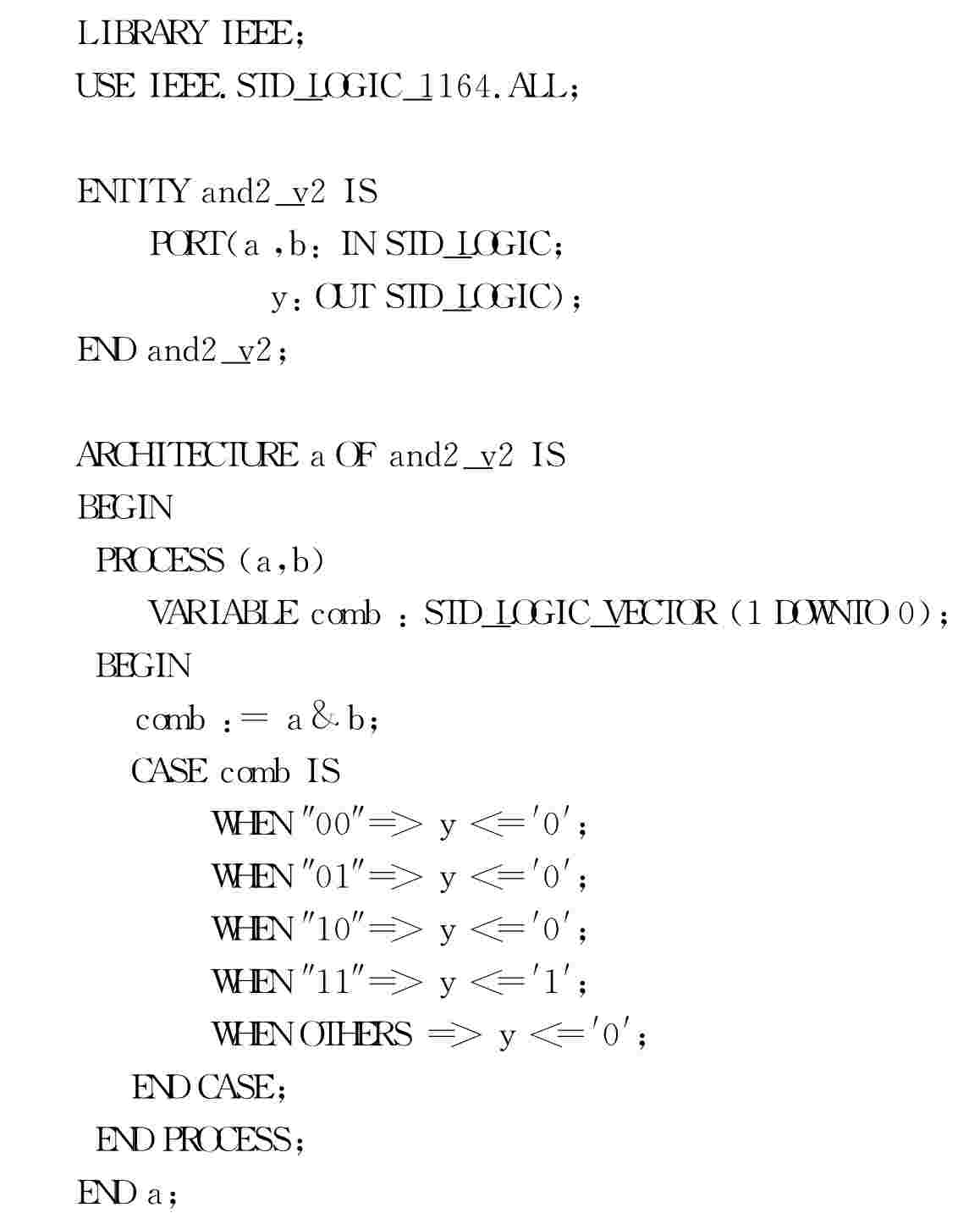

(2)两输入与门的行为描述

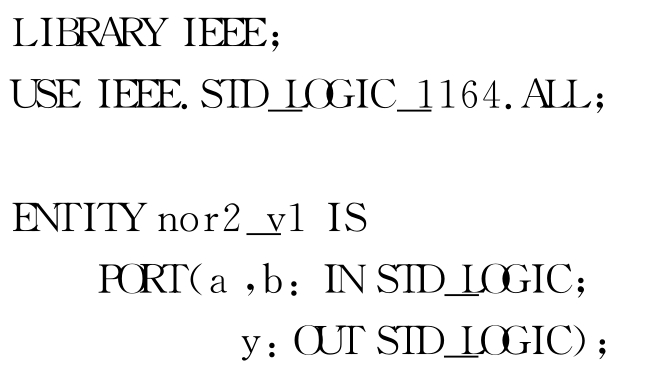

3.两输入或非门电路

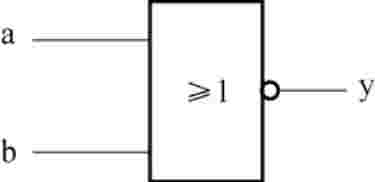

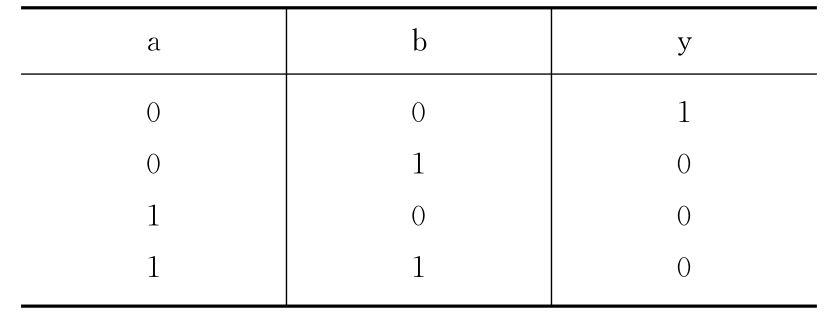

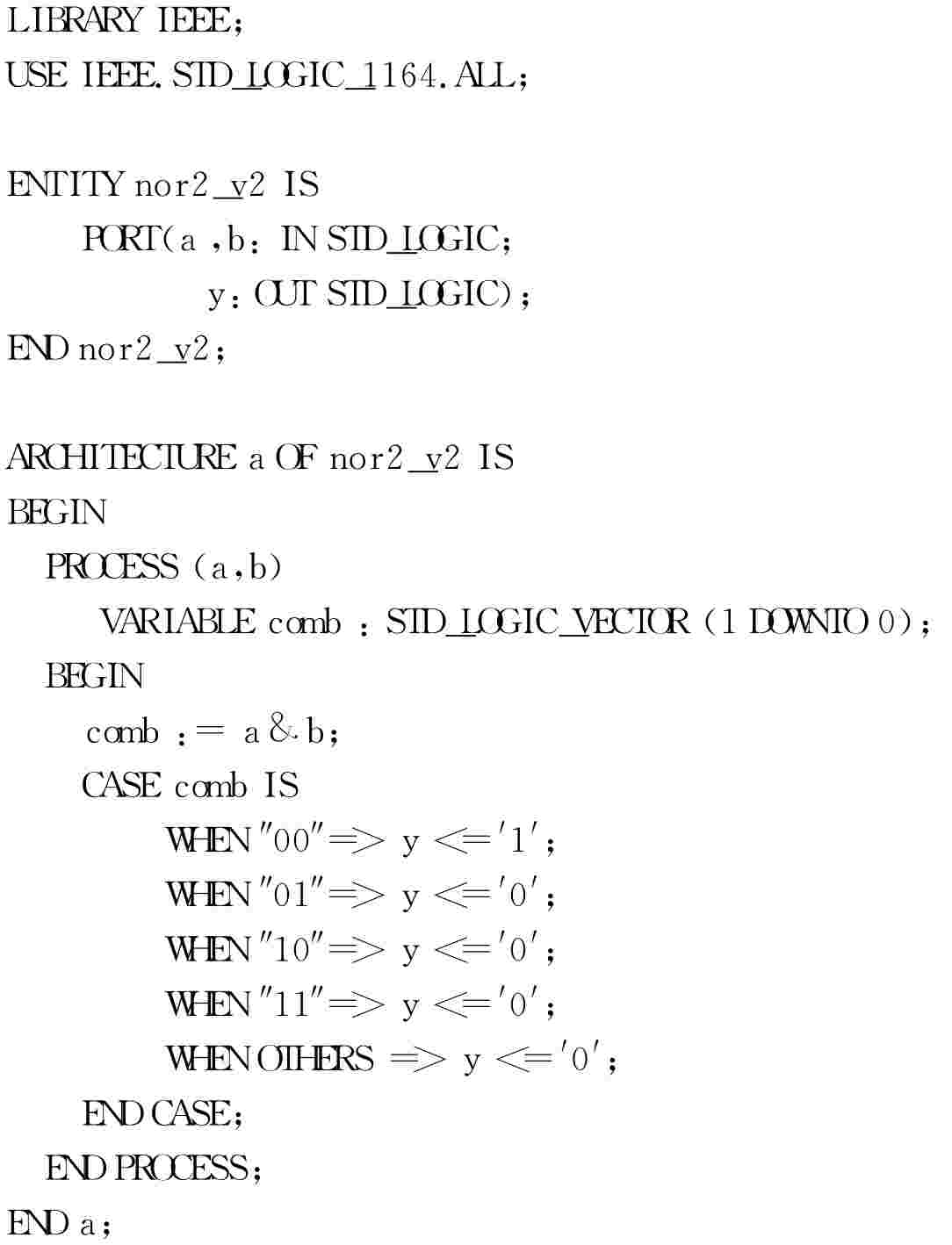

两输入或非门的逻辑表达式为:y=a+b,其逻辑电路图如图3-3,真值表如表3-3。

图3-3 两输入或非门的逻辑电路图

表3-3 两输入或非门的真值表

(1)两输入或非门的数据流描述

(2)两输入或非门的行为描述

4.两输入异或门电路

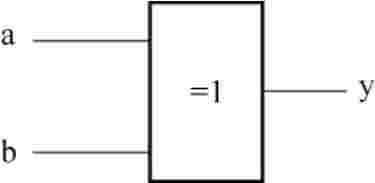

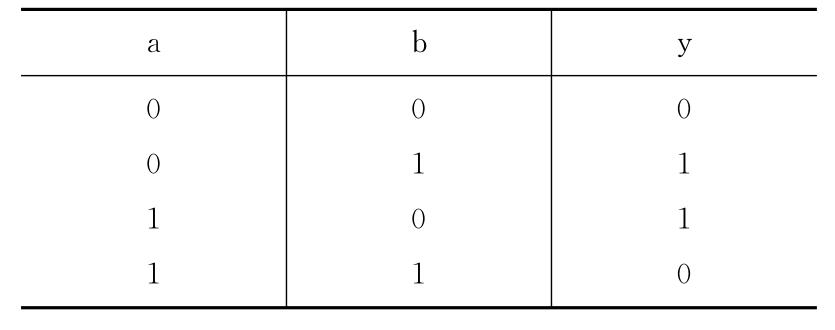

两输入异或门的逻辑表达式为:y=a+b=a-b+ab,其逻辑电路图如图3-4,真值表如表3-4。

图3-4 两输入异或门的逻辑电路图

表3-4 两输入异或门的真值表

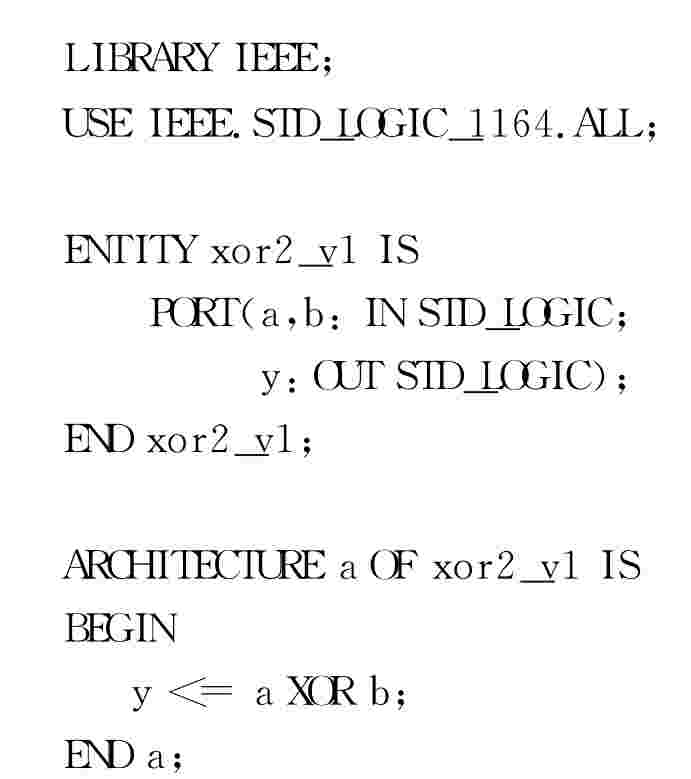

(1)两输入异或门的数据流描述

上面的描述也可以写为:y<=(a AND NOT b)OR(NOT a AND b);

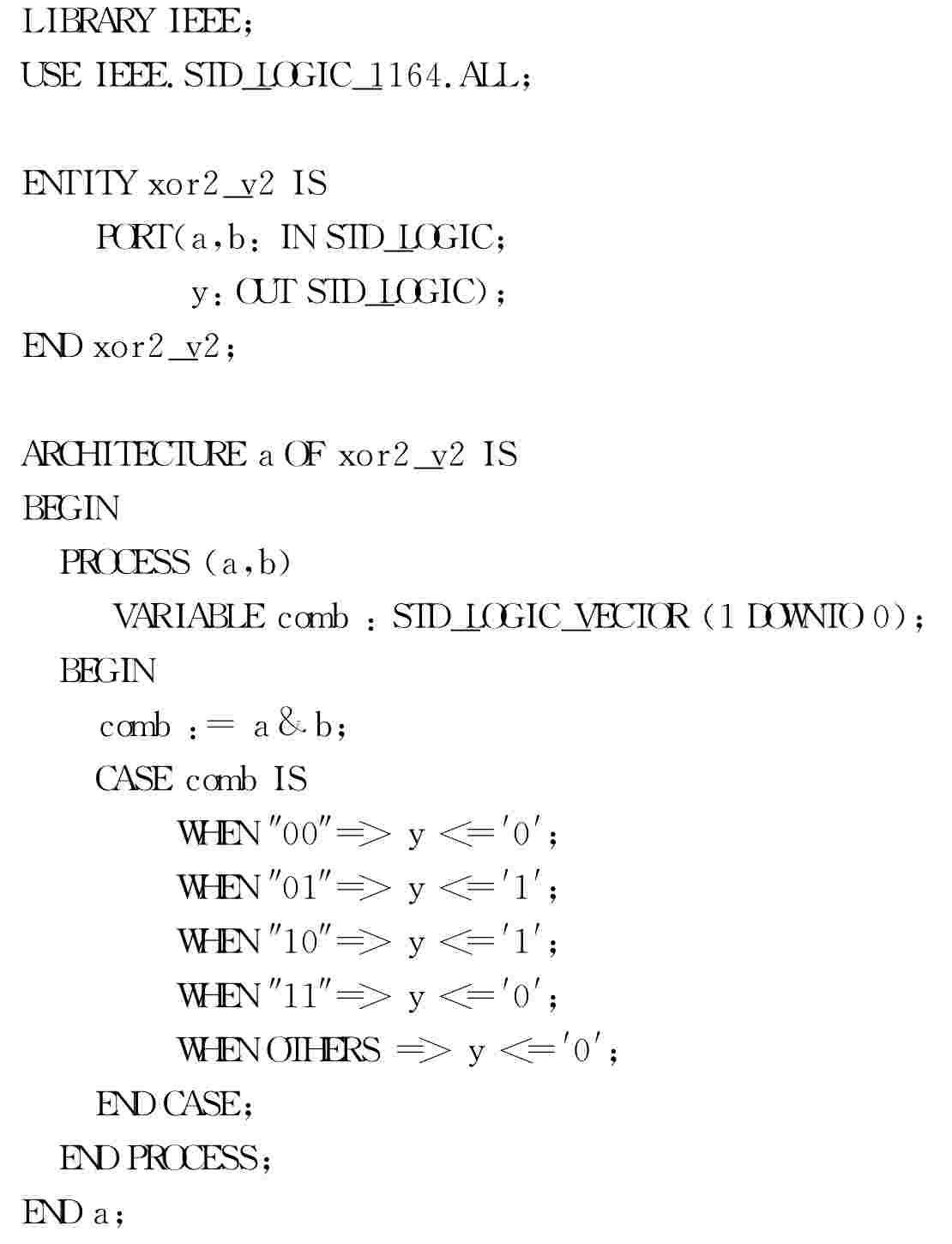

(2)两输入异或门的行为描述

上一篇:制造费用分配表的分配率怎么填写

.jpg)

.jpg)