实验3 译码器及其应用

【实验目的】

(1)掌握中规模集成译码器的逻辑功能和使用方法;

(2)熟悉实验板的结构和使用方法。

【实验所用仪器及元器件】

(1)计算机;

(2)直流稳压电源;

(3)数字电路实验板;

(4)74LS138、74LS00。

【实验原理】

译码器是一个多输入、多输出的组合逻辑电路。它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配、存贮器寻址和组合控制信号等,不同的功能可选用不同种类的译码器。

其中,最常见的译码器是变量译码器,又称二进制译码器,如2线—4线、3线—8线和4线—16线译码器。若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用,而每一个输出所代表的函数对应于n个输入变量的最小项。

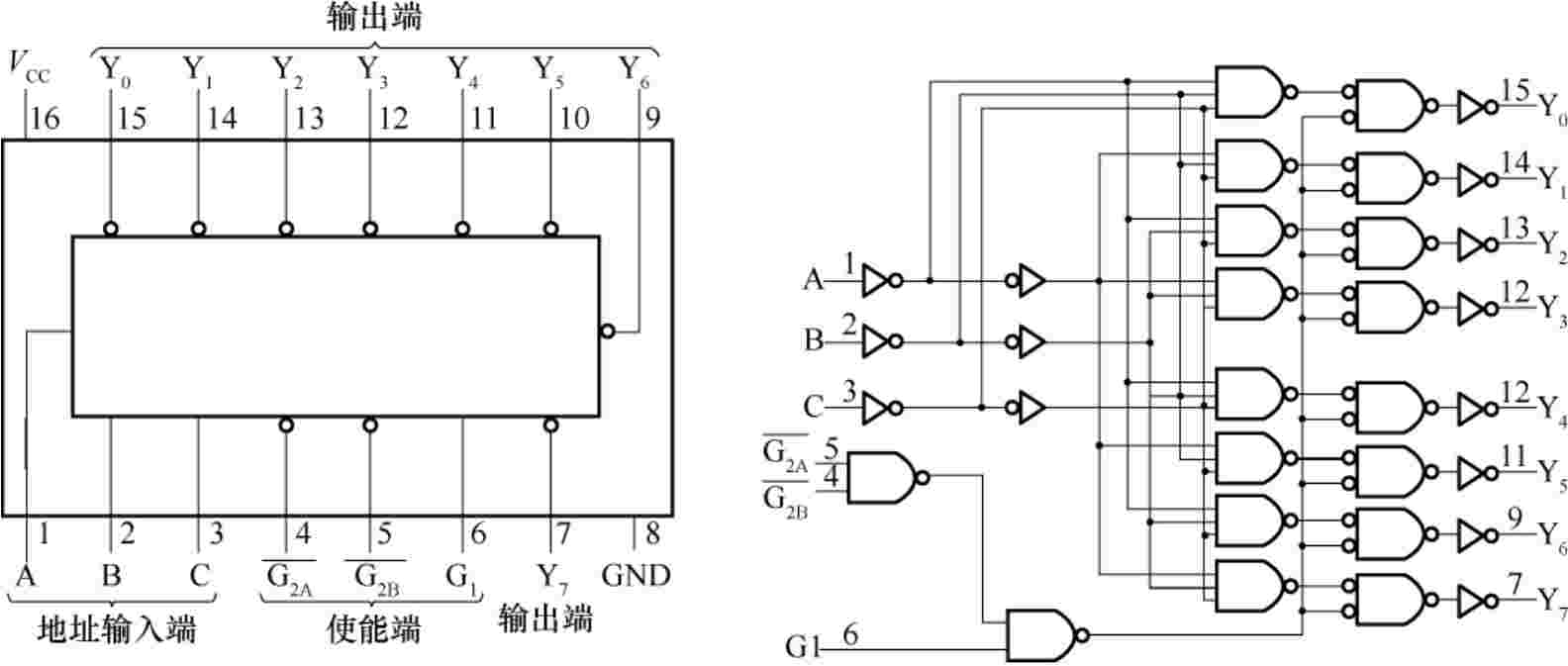

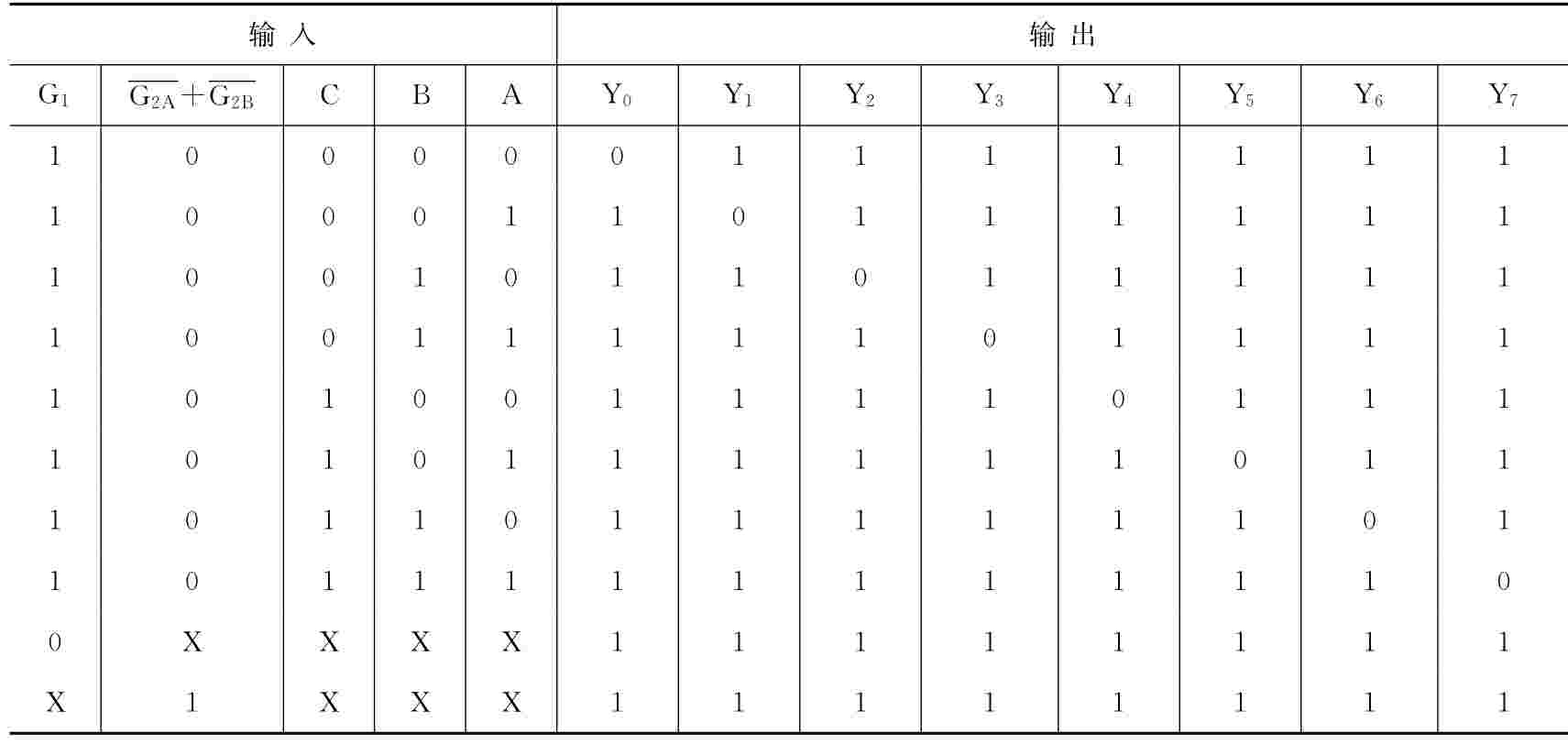

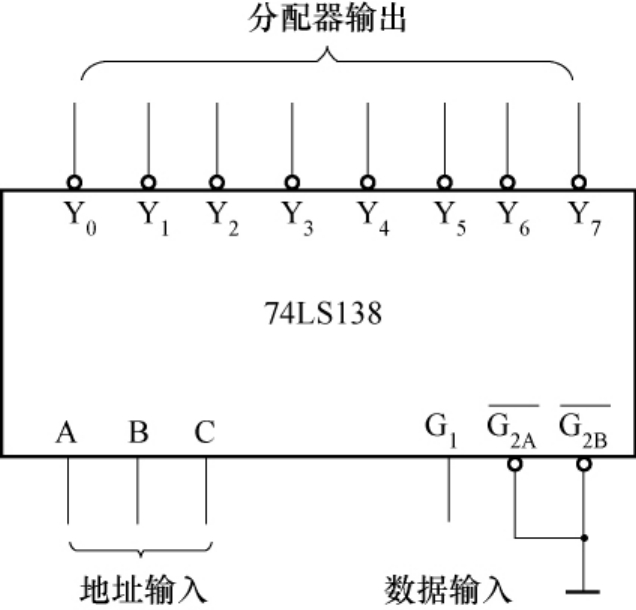

以3线—8线译码器74LS138为例进行分析,图6-9为其引脚排列图及逻辑图,表6-8 是74LS138的真值表。

图6-9 3线—8线译码器74LS138引脚排列图及逻辑图

表6-8 74LS138的真值表

74LS138是一个16脚的双列直插式集成电路,第16脚接电源正极,第8脚接地。A、 B、C为地址输入端,Y0~Y7为译码器输出端,G1、 为使能端。当G1=1,

为使能端。当G1=1, =0时,和译码器处于正常工作状态,地址端所指定的输出端有信号(0)输出,其它所有输出端均无信号(全为1)。当G1=0,

=0时,和译码器处于正常工作状态,地址端所指定的输出端有信号(0)输出,其它所有输出端均无信号(全为1)。当G1=0, =X时,或G1=1

=X时,或G1=1 =1,译码器被禁止,所有输出同时为1。

=1,译码器被禁止,所有输出同时为1。

二进制译码器实际上也是负脉冲输出的脉冲分配器。若利用使能端中的一个输入端输入数据信息,器件就成为一个数据分配器(又称多路分配器),如图6-10所示。若在G1输入端输入数据信息, =0地址码所对应的输出是G1数据信息的反码;若从

=0地址码所对应的输出是G1数据信息的反码;若从 端输入数据信息,令G1=1,G2B=0地址码所对应的输出就是G2A端数据信息的原码。若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。

端输入数据信息,令G1=1,G2B=0地址码所对应的输出就是G2A端数据信息的原码。若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。

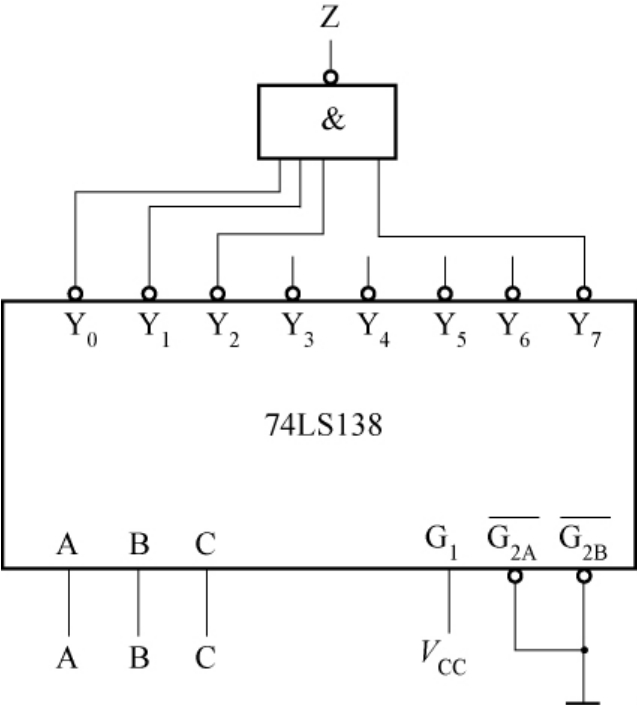

二进制译码器还能方便地实现逻辑函数,如图6-11所示,实现的逻辑函数是Z= +

+ +A

+A +ABC。

+ABC。

图6-10 译码器做数据分配器

图6-11 译码器实现逻辑函数

【实验内容】

1.74LS138译码器逻辑功能测试

将译码器使能端G1 及地址端A、B、C分别接至拨码开关,8个输出端Y0~Y7依次连接在发光二极管LD0~LD7上,改变使能端和地址端的值,按表6-8逐项测试74LS138的逻辑功能。

及地址端A、B、C分别接至拨码开关,8个输出端Y0~Y7依次连接在发光二极管LD0~LD7上,改变使能端和地址端的值,按表6-8逐项测试74LS138的逻辑功能。

2.用74LS138和74LS00实现逻辑函数 ,用拨码开关作为输入,用发光二极管显示输出。

,用拨码开关作为输入,用发光二极管显示输出。

上一篇:交易结构的设计

下一篇:高校“推优”工作的重要意义

.jpg)

.jpg)