17.7 逻辑分析仪

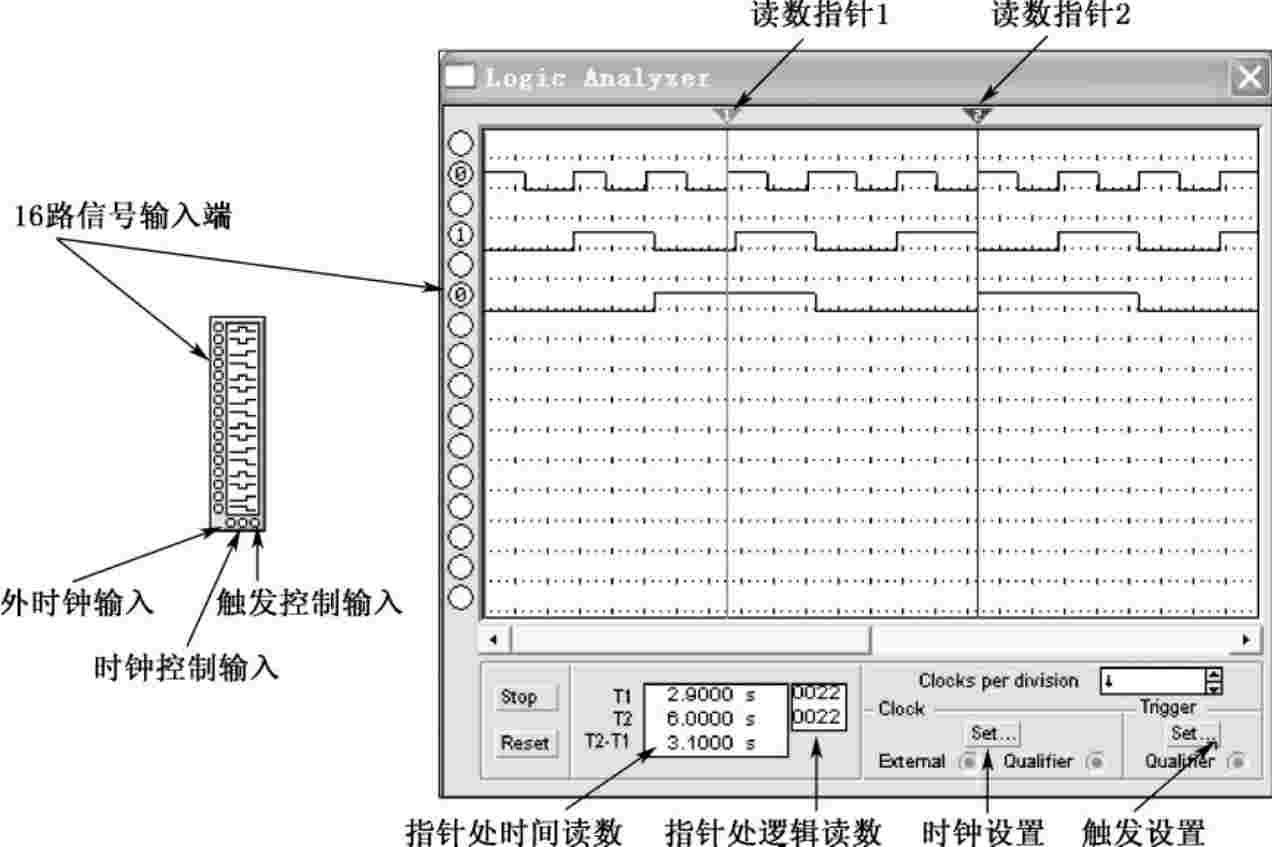

EWB提供了16路的Logic Analyzer(逻辑分析仪),显示方式分为图形方式和十六进制两种。仿真逻辑分析仪与实际的逻辑分析仪的使用及控制方式一样。逻辑分析仪的图标如图17.19所示。逻辑分析仪的连接端口有:外接时钟端、时钟定时器、触发定时器以及16路信号输入端。

图17.19 逻辑分析仪的图标

1)逻辑分析仪的面板

双击逻辑分析仪图标,屏幕显示出逻辑分析仪的面板,如图17.19所示。面板分上下两个部分:上半部分是被测信号的显示窗口,下半部分是逻辑分析仪的控制窗口。主要控制信号有:Stop(停止)、Reset(复位)、Clock(时钟)设置和Trigger(触发)设置。逻辑分析仪还有一个小窗口,显示T1(左侧游标)的位置和数据、T2(右侧游标)的位置和数据以及两游标之间的时间(T2-T1)。

2)逻辑分析仪的位置

(1)Stop(停止)键:逻辑分析仪正在显示数据时,Stop无效;当逻辑分析仪没有开始触发时,单击Stop可以调入预先存储的数据。

(2)Reset(复位)键:单击Reset,清除逻辑分析仪显示的数据。

(3)Clock(时钟):单击Clock框的Set(设置)时,将会出现Clock setup(时钟设置)对话框,如图17.20所示。

图17.20 “逻辑分析仪时钟设置”对话框

其中可以选择的时钟设置有:

①Clock edge(时钟边沿):可以选择上升沿或下降沿。

②Clock mode(时钟模式):可以选择内触发或外触发。

③Internal clock rate(内部时钟频率):可以在1~999Hz范围内选择。

④Clock qualifier(时钟定时器):可以在0、1或X中间进行选择。

⑤Logic analyzer(逻辑分析仪):可以设置Pre-trigger samples(触发前取样点)、Post-trigger samples(触发后取样点)和Threshold voltage(开启电压)。

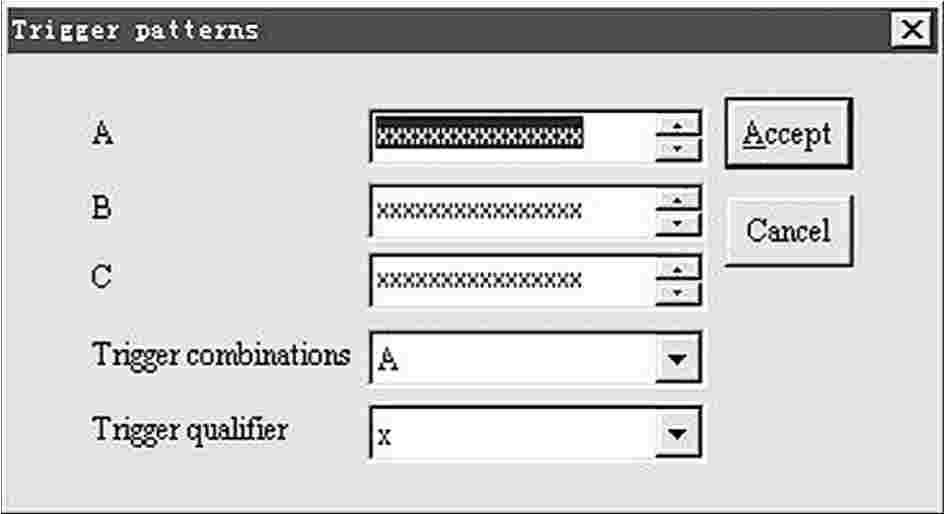

(4)Trigger(触发):单击Trigger框的Set(设置)时,将会出现“Trigger patterns(触发模式)”对话框,如图17.21所示。可以用三个变量A、B、C来定义触发限制和触发模式,在触发模式栏目下有八种触发模式可供选择。

图17.21 逻辑分析仪“触发模式”设置对话框

(5)Clocks per division(每格时钟):逻辑分析仪时间基准的取值范围为1~128s/div。

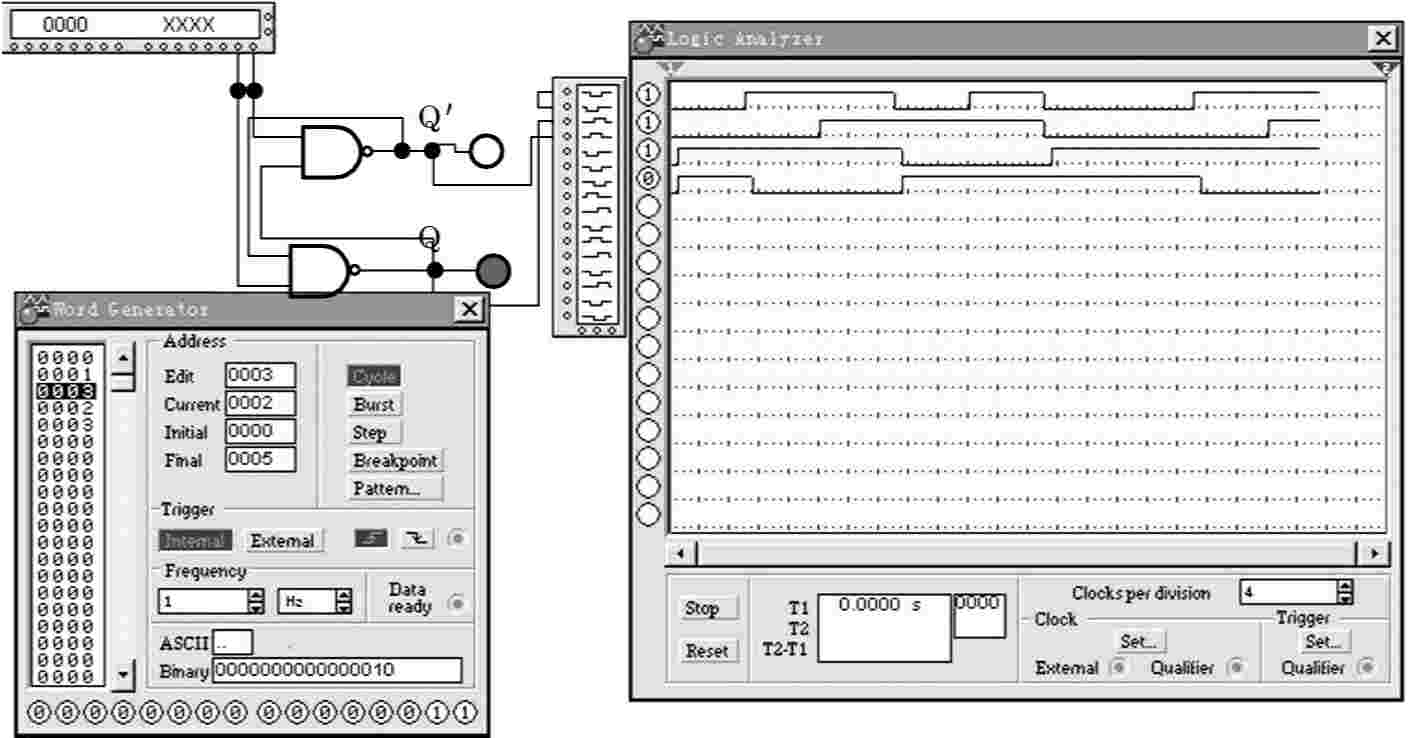

3)逻辑分析仪的连接

连接一个基本RS触发器,在该电路的R端和S端加入两路字符发生器产生的字符信号。为了观察触发器在输入信号作用下输出状态的变化情况,可以将触发器的两路输入信号和两路输出信号分别连到逻辑分析仪的输入端,连接方式如图17.22所示。

图17.22 逻辑分析仪的使用示例

4)测试结果的观察

(1)双击字符发生器图标,根据RS触发器的原理设置字符输入顺序:0000→0001→0003→0002→0003→0000,设置时钟频率为1Hz,设置起始地址为0000,结束地址为0005。

(2)双击逻辑分析仪图标,根据字符发生器的频率,设置逻辑分析仪的时钟频率为10Hz,时间基准为4s/div,合理设置逻辑分析仪的两个触发取样点。例如,可以将Pre-trigger samples设为10,将Post-trigger samples设为100。

(3)单击字符发生器的Cycle(周期)按钮,在逻辑分析仪的显示窗口,可以看到RS触发器输入信号改变时输出信号的变化情况,如图17.22所示。

面板左边的16个小圆圈对应16个输入端,从上到下依次为最低位至最高位。小圆圈内动态变化数值为实时显示逻辑信号当前值。逻辑信号波形显示区以方波方式显示16路逻辑信号的波形。通过设置输入导线的颜色可以修改相应波形的显示颜色。波形显示的时间轴刻度可通过面板下边的Clock PerDivision予以设置。拖拽读数指针可读取指针处波形数据。在面板下部的两个方框内显示指针处位置的时间读数和逻辑读数(4位十六进制数)。任何时候单击Reset按钮,逻辑分析仪就会复位,显示和波形被清除。

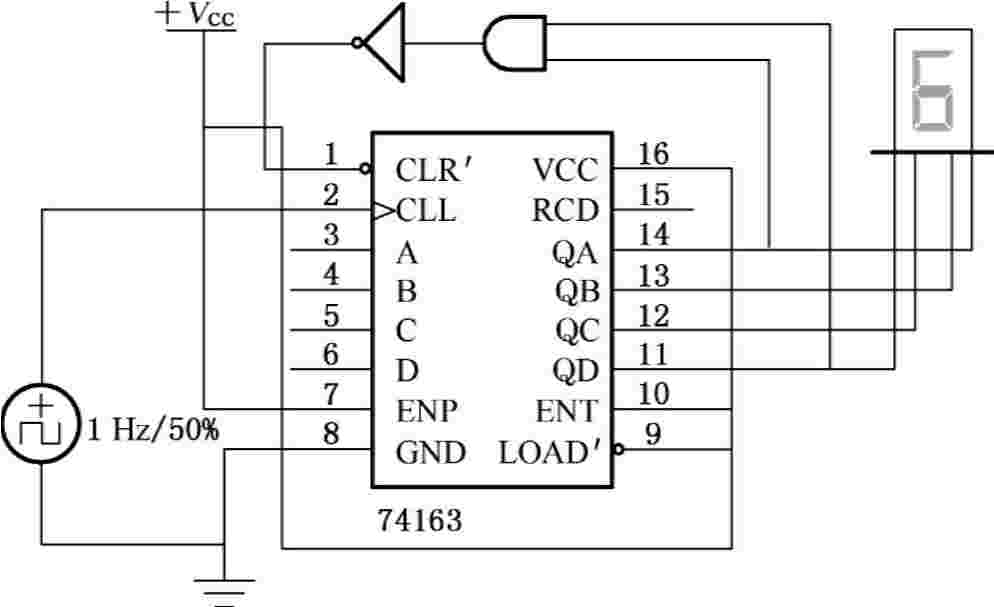

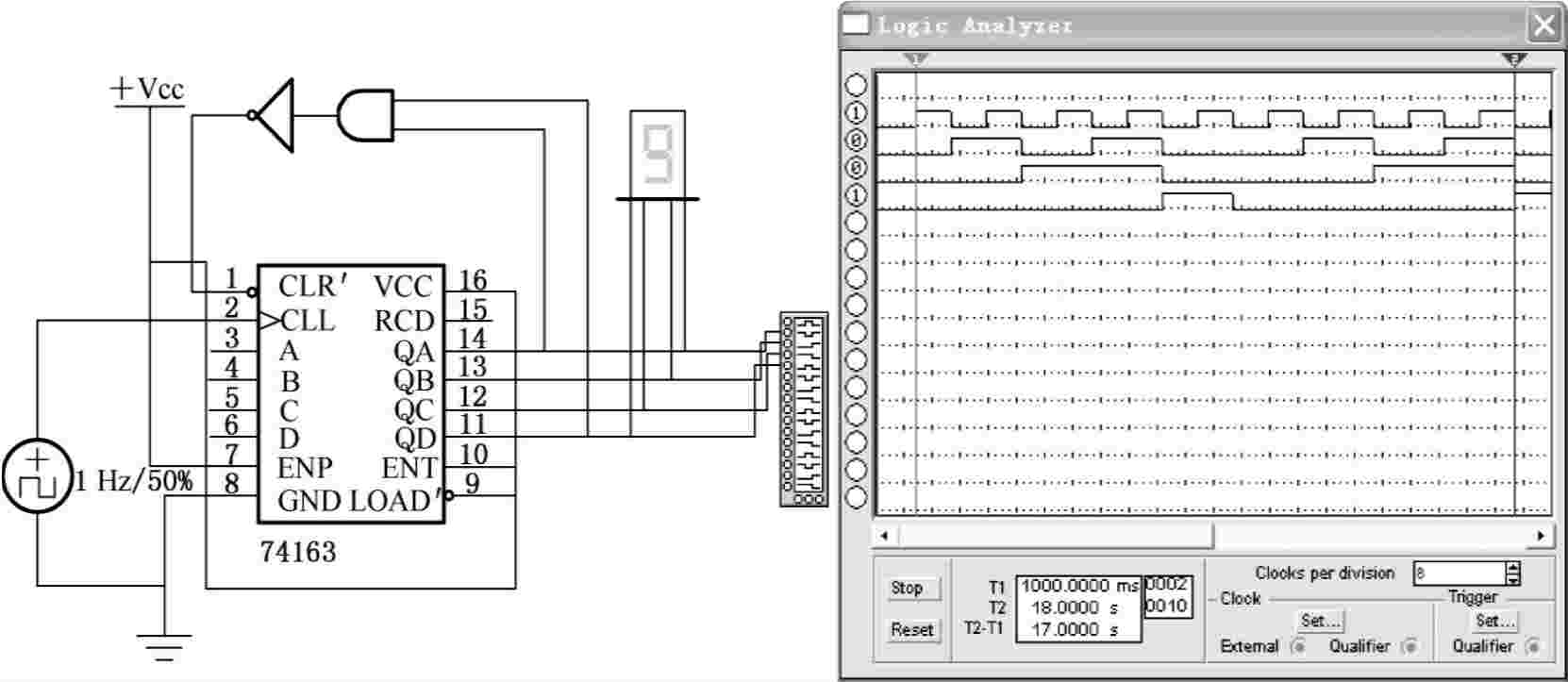

例:如图17.23所示是由74164同步4位二进制集成计数器构成的十进制计数电路,试用逻辑分析观测该电路输出QA、QB、QC、QD的波形。

图17.23 74164构成的十进制计数器电路

逻辑分析仪的连接图和观测输出波形如图17.24所示。

图17.24 十进制计数器电路输出波形

.jpg)

.jpg)